EPM570T100C5N CPLDs: Features, Applications and Datasheet

2025-09-29 11:00:10 1721

EPM570T100C5N Description

The EPM570T100C5N is a member of the Altera MAX II CPLD family, designed to provide cost-effective, non-volatile programmable logic with higher logic density compared to traditional CPLDs. It integrates up to 570 macrocells, embedded memory, and fast I/O capabilities in a compact 100-pin TQFP package. Unlike FPGAs that require external configuration memories, the MAX II family uses on-chip flash configuration, ensuring instant-on performance and low power operation, making it suitable for control-intensive and glue-logic applications.

EPM570T100C5N Features

Logic Density: 570 macrocells, equivalent to ~4400 logic elements in complexity.

On-Chip Flash Memory: Non-volatile configuration with instant-on capability.

Embedded Memory: 8 M4K RAM blocks for small buffer and state machine storage.

I/O Capability: Up to 76 user I/O pins, supporting multiple voltage standards (1.5V to 3.3V).

Low Power Consumption: Static power as low as 200 mW typical.

Package: 100-pin TQFP (T100).

Clock Management: Support for global clock networks and fast routing for timing-critical designs.

In-System Programming (ISP): JTAG support for easy updates and debugging.

EPM570T100C5N Applications

System Glue Logic: Interfacing between multiple ICs in communication or embedded systems.

I/O Expansion: Extending microcontroller or processor I/O capabilities.

State Machine Control: Handling sequencing and decision-making logic in automation or industrial electronics.

Power Management Systems: Supervisory control, sequencing, and monitoring of power rails.

Communication Equipment: Protocol bridging, bus interfacing, and control-plane logic.

Consumer & Industrial Electronics: Compact, reliable replacement for discrete logic designs.

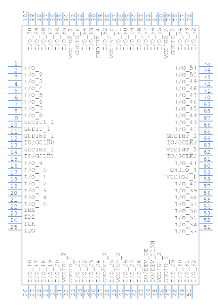

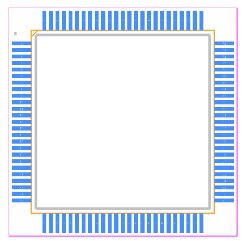

EPM570T100C5N CAD Model

Symbol

Footprint

3D Model

EPM570T100C5N Alternatives

If the EPM570T100C5N is not available, consider:

EPM570T144C5N – Same density but with a 144-pin TQFP package for more I/Os.

EPM240T100C5N – Lower-density MAX II CPLD with 240 macrocells for cost-sensitive applications.

XC2C512 (Xilinx CoolRunner-II) – Similar density, low-power CPLD with non-volatile architecture.

ATF1508ASV (Microchip/Atmel) – High-density CPLD alternative with flash-based configuration.

Intel MAX 10 FPGA – For projects needing CPLD-style non-volatile configuration but with FPGA flexibility.

EPM570T100C5N Manufacturer

Intel Corporation is a global leader in semiconductor innovation, best known as one of the world’s largest and most influential microprocessor manufacturers. Founded in 1968 by Robert Noyce and Gordon Moore, Intel pioneered the development of the x86 architecture, which has become the foundation for most of today’s personal computers, servers, and data center systems.

Headquartered in Santa Clara, California, Intel designs and manufactures a broad portfolio of technologies, including microprocessors, chipsets, graphics, networking components, memory, programmable logic devices (FPGAs), and advanced foundry services. Beyond PCs, Intel plays a critical role in powering cloud computing, 5G networks, artificial intelligence, autonomous driving, and edge devices, shaping the future of digital transformation.

With its emphasis on process technology leadership, high-performance computing, and energy-efficient design, Intel continues to drive advancements across consumer, enterprise, and industrial markets. Its well-known product families include Intel® Core™ processors, Xeon® server CPUs, Intel® FPGA solutions (via Altera acquisition), and Intel® Foundry Services, which provide custom silicon manufacturing for global customers.

EPM570T100C5N FAQs

1. How does the instant-on feature of the EPM570T100C5N benefit real-time applications?

Because the device uses on-chip flash configuration, it powers up and starts functioning immediately without waiting for external configuration loading, which is critical for reset controllers, power sequencing, and industrial control systems.

2. What type of embedded memory resources are available, and how can they be used?

The device includes M4K RAM blocks, which can be configured as FIFO buffers, small lookup tables, or temporary storage for communication protocols, reducing the need for external RAM in compact systems.

3. How many programmable I/Os does the EPM570T100C5N support, and can they handle mixed voltage operation?

The CPLD supports up to 76 user I/O pins in its 100-pin TQFP package. It allows mixed-voltage I/O operation across different banks, supporting standards like LVTTL, LVCMOS, PCI, and 3.3V/2.5V signaling.

4. Is in-system programmability supported, and what interface is required?

Yes, the device can be fully configured and debugged through a JTAG interface, enabling field updates and reducing the need for external programmers or chip replacements.

5. What are the speed and power trade-offs of the -5 speed grade in this device?

The -5 speed grade represents a balanced performance option, offering moderate clock-to-output delays and lower static power consumption. For faster timing closure, a -4 grade could be considered, but at slightly higher power.